### **HD 61810**

High Performance Signal Processor (HSP)

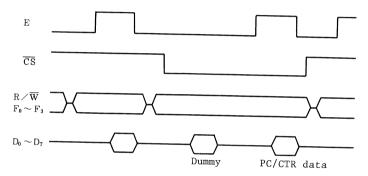

### HITACHI DIGITAL SIGNAL PROCESSOR(HSP) HD61810 USER'S MANUAL

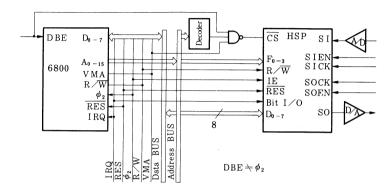

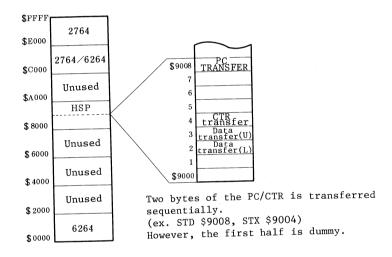

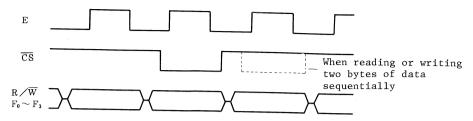

#### JAN. 1986 AD-ED091

When using this manual, the reader should keep the following in mind;

- 1. This manual may, wholly or partially, be subject to change without notice.

- All rights reserved: No one is permitted to reproduce or duplicate, in any form, the whole or part of this manual without Hitachi's permission.

- 3. Hitachi will not be responsible for any damage to the user that may result from accidents or any other reasons during operation of his unit according to this manual.

- 4. This manual neither ensures the enforcement of any industrial properties or other rights, nor sanctions the enforcement right thereof.

Copyright © Hitachi, Ltd. 1985. All rights reserved.

#### CONTENTS

| 1. | GENE | RAL DESC | CRIPTIONS                                       | 1       |

|----|------|----------|-------------------------------------------------|---------|

|    | 1.1  | HSP KE   | Y FEATURES                                      | 3       |

|    | 1.2  | APPLICA  | ATIONS                                          | 6       |

|    |      |          |                                                 | 7       |

| 2. | ARCH |          | E                                               | 9       |

|    | 2.1  |          | NCTIONS                                         | 9<br>14 |

|    | 2.2  |          | AL RESOURCES                                    | 17      |

|    | 2.3  | MEMORY   |                                                 |         |

|    |      | 2.3.1    | Configuration                                   | 17      |

|    |      | 2.3.2    | Instruction ROM                                 | 18      |

|    |      | 2.3.3    | Data RAM                                        | 18      |

|    |      | 2.3.4    | Data ROM                                        | 21      |

|    |      | 2.3.5    | General Register (GR)                           | 22      |

|    |      | 2.3.6    | Memory Addressing Mode                          | 23      |

|    |      | 2.3.7    | Memory Data Format                              | 24      |

|    |      | 2.3.8    | Precaution in Using ROM/RAM Memory              | 25      |

|    | 2.4  | REGIST   | ERS                                             | 26      |

|    |      | 2.4.1    | Program Counter (PC)                            | 26      |

|    |      | 2.4.2    | Stack Registers (STACKO and STACK1)             | 26      |

|    |      | 2.4.3    | Accumulators (ACCA and ACCB)                    | 27      |

|    |      | 2.4.4    | Condition Code Register (CCR)                   | 29      |

|    |      | 2.4.5    | Control Register (CTR)                          | 30      |

|    |      | 2.4.6    | Status Register (STR)                           | 31      |

|    |      | 2.4.7    | Repeat Counter (RC)                             |         |

|    |      | 2.4.8    | Address Pointers (RAM Pointer A/B, ROM Pointer) |         |

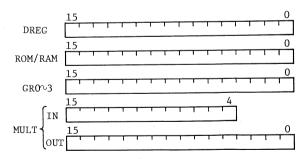

|    |      | 2.4.9    | Delay Register (DREG)                           | 36      |

| 3. | 1/0  | INTERFA  | ACE                                             | 39      |

|    | 3.1  | T /O TI  | NTERFACE                                        | 41      |

|    | 3.1  | 3.1.1    |                                                 | 41      |

|    |      | 3.1.2    |                                                 |         |

|    | 3.2  | -        | RUPT                                            |         |

|    | 3.3  |          | DIRECT MEMORY ACCESS)                           |         |

|    | 2.2  |          | /o                                              |         |

| 4.  | ARITHMETIC OPERATION                             | 61       |

|-----|--------------------------------------------------|----------|

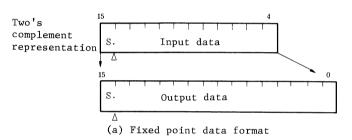

|     | 4.1 DATA FORMAT                                  | 63       |

|     | 4.2 FIXED POINT ARITHMETIC                       | 65       |

|     | 4.2.1 Fixed Point ALU                            | 65       |

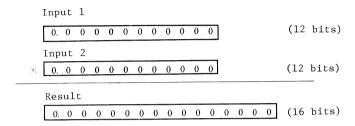

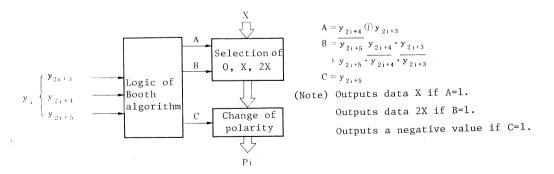

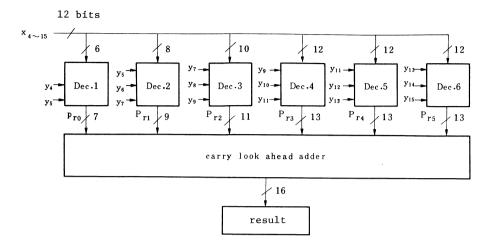

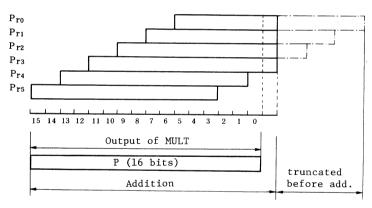

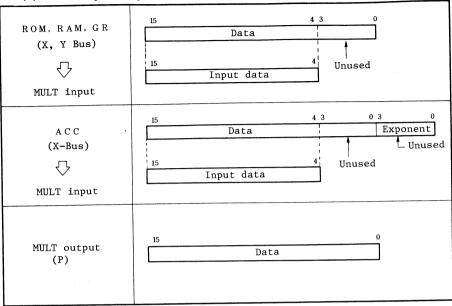

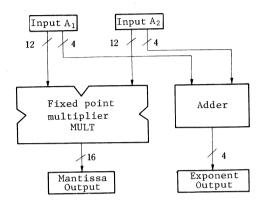

|     | 4.2.2 Fixed Point Multiplication                 | 67       |

|     | 4.3 FLOATING POINT ARITHMETIC                    | 71       |

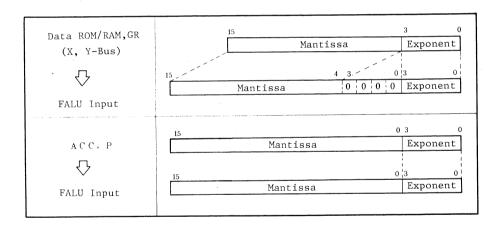

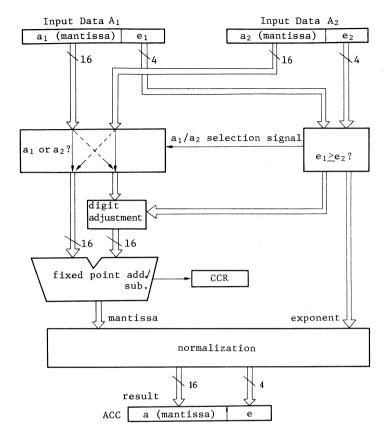

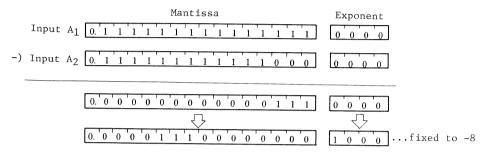

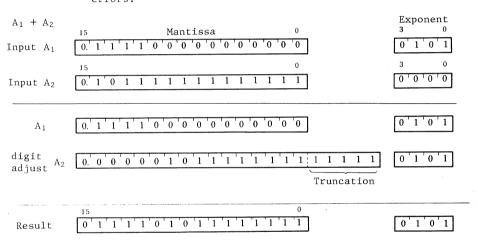

|     | 4.3.1 Floating Point ALU (FALU)                  | 71       |

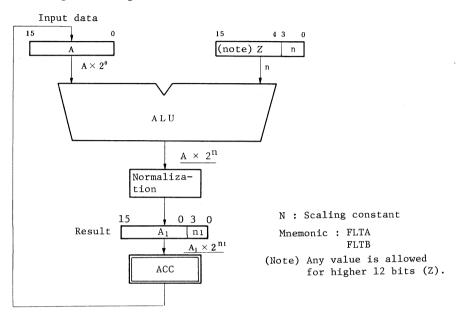

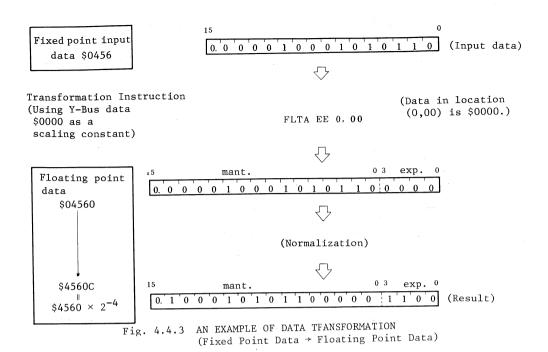

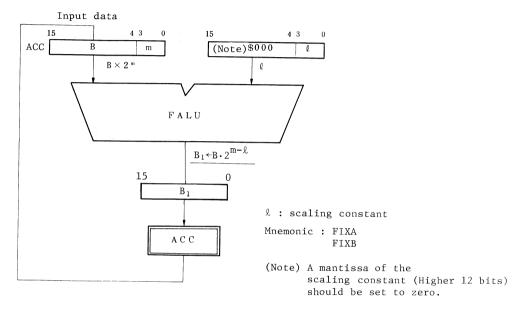

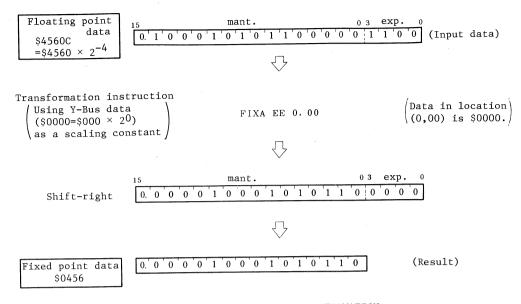

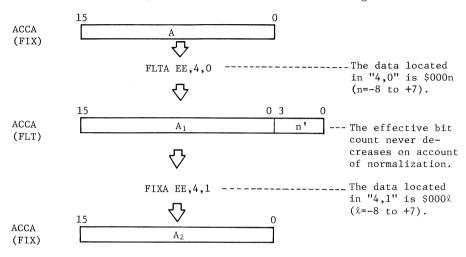

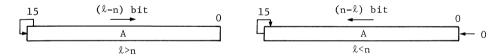

|     | 4.4 DATA TRANSFORMATION                          | 77<br>79 |

|     |                                                  | 7 9      |

| 5.  | INSTRUCTION                                      | 85       |

|     | 5.1 GENERAL DESCRIPTION                          | 87       |

|     | 5.2 INSTRUCTION SET                              | 88       |

|     |                                                  | 234      |

|     |                                                  | 238      |

|     | 5.3 PIPELINE CONTROL                             | 243      |

| 6.  | PROGRAMMING TECHNIQUE                            | 247      |

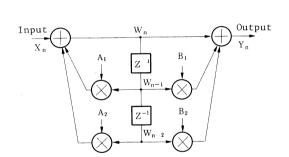

|     | 6.1 BIQUAD FILTER                                | 249      |

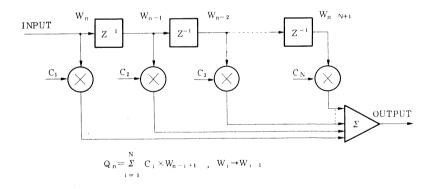

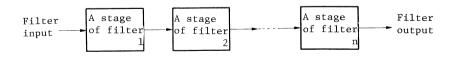

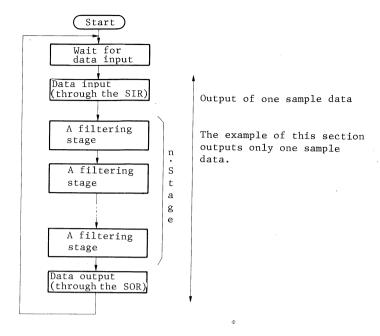

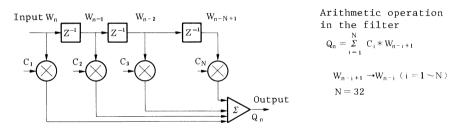

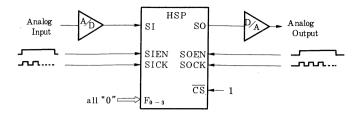

|     | 6.2 TRANSVERSAL FILTER                           | 251      |

| 7.  | HSP APPLICATION                                  | 253      |

| 8.  | ELECTRICAL CHARACTERISTICS AND PACKAGE OUTLINE 2 | 265      |

|     | 8.1 ABSOLUTE MAXIMUM RATING                      | 267      |

|     | 8.2 ELECTRICAL CHARACTERISTICS 2                 | 267      |

|     | 8.3 PACKAGE OUTLINE                              | 273      |

| лрр | DEMINITY                                         | . 7.5    |

|     |                                                  | 275      |

| 1.  | HSP REGISTER MODEL 2                             | 77       |

| 2.  | INSTRUCTION CODE                                 | 79       |

| 3.  | INSTRUCTION SET                                  | 82       |

| 4.  | ASSEMBLER SYNTAX 2.                              | 84       |

| 5.  | HSP INSTRUCTION SUMMARY                          | 87       |

| 6.  | MEMORY MAP                                       | 88       |

| 7.  | HSP ORDERING SPECIFICATION                       |          |

| 8.  | TEST PROGRAM                                     |          |

|     |                                                  |          |

# SECTION 1 GENERAL DESCRIPTIONS

#### GENERAL DESCRIPTIONS

#### 1.1 HSP KEY FEATURES

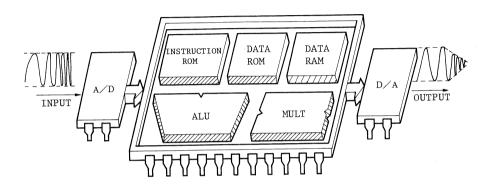

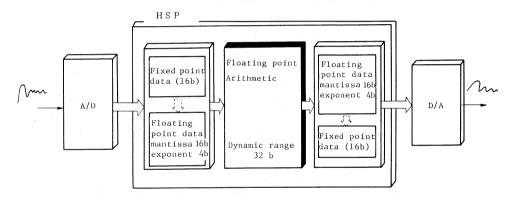

A High Performance Signal Processor (HSP) is a single chip processor with a stored program designed for a high speed digital signal processing. The HSP contains a high speed floating point arithmetic unit and performs an operation (addition/subtruction/multiplication) with an instruction in a single cycle of only 250 ns. Moreover, the HSP employs a CMOS process to realize a low power consumption.

- 3 μm CMOS technology

- Arithmetic

- Floating point arithmetic

- Pipeline control

- Horizontal microinstructions

- Large capacity memories

- 200 × 16-bit data RAM (2-port accessible)

- 128 × 16-bit data ROM

- 512 × 22-bit instruction ROM

- System bus compatible with 8/16-bit microcomputer

- DMA operation between the HSP and external memory

- Serial I/O interface for up to 16 bits

- Operation speed

- Input clock

- ; 16 MHz

- Internal clock

- : 4 MHz

- Instruction cycle; 250 ns

- MULT, ALU

- ; 250 ns

(throughput with pipeline control)

- A single power supply of +5V

- Low power dissipation of 250 mW typ.

- Two levels of subroutine and interrupt

- $\blacksquare$  Interrupt by three factors (end of three kinds of data I/0 transfer)

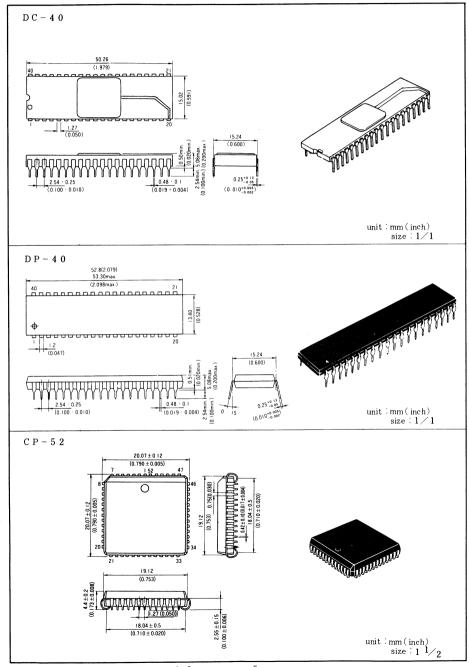

- Package; DIC-40/DIP-40/PLCC-52

#### ● What Is The Floating Point Arithmetic ?

The floating point arithmetic expresses a number with a mantissa and an exponent as follows;

$n = a \cdot 2^b$  (a; mantissa, b; exponent)

The floating point arithmetic allows a wide range of numbers to be expressed with less bits, and realizes an easy programming without digit adjustment.

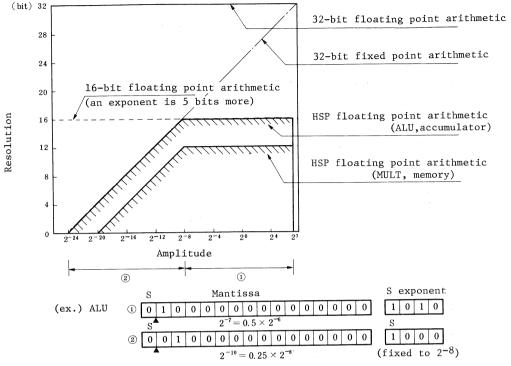

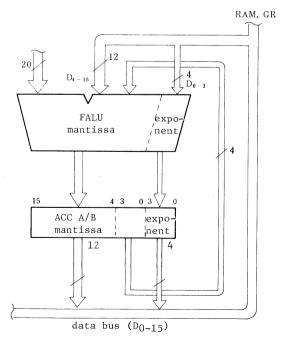

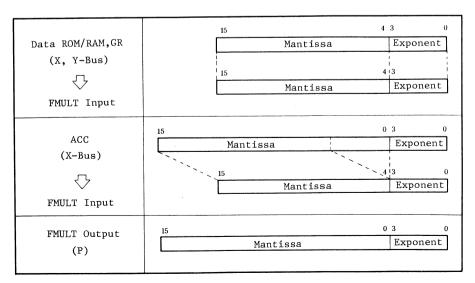

The HSP provides 16 bits for mantissa and 4 bits for exponent and can always work in the maximum precision (16 bits).

In the ALU and an accumulator, the mantissa is 16 bits and the exponent is 4 bits, while in multiplier and memory, the mantissa is 12 bits and the exponent is 4 bits. These data formats allow the HSP to have the precision given by the hatches in Fig. 1.1.1 in the floating point operation. As the exponent is 4 bits, it is fixed to -8 when the data amplitude is low. Therefore, the effective bit length varies in proportion to the data amplitude. When the data exceeds 2-8, the mantissa is normalized and the exponent varies; the effective bit length is fixed to 16 bits maximum.

As described above, the HSP realizes a 32-bit dynamic range with 16 bits of the mantissa and 4 bits of the exponent.

Fig. 1.1.1 HSP FLOATING POINT ARITHMETIC

#### • What Is The Pipeline Control ?

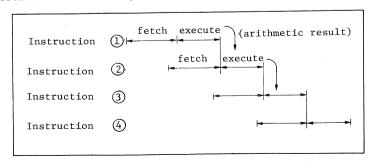

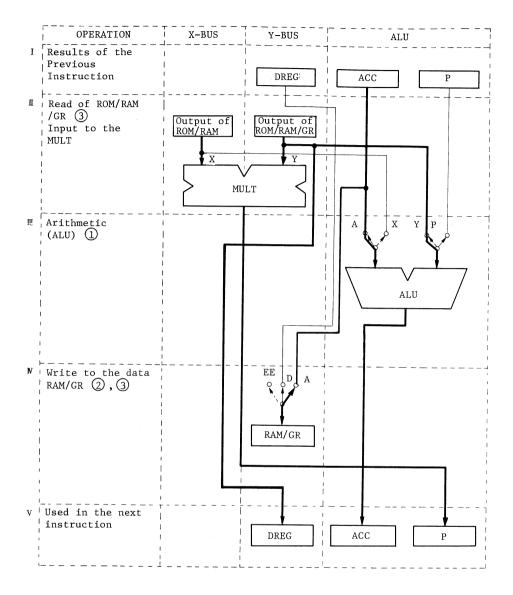

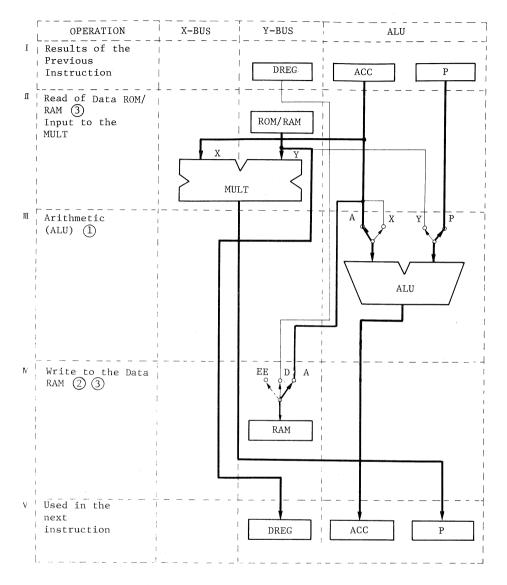

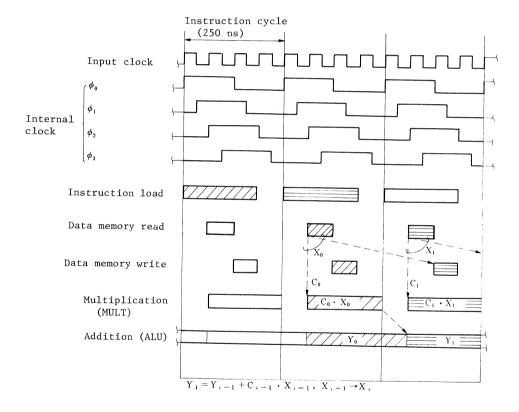

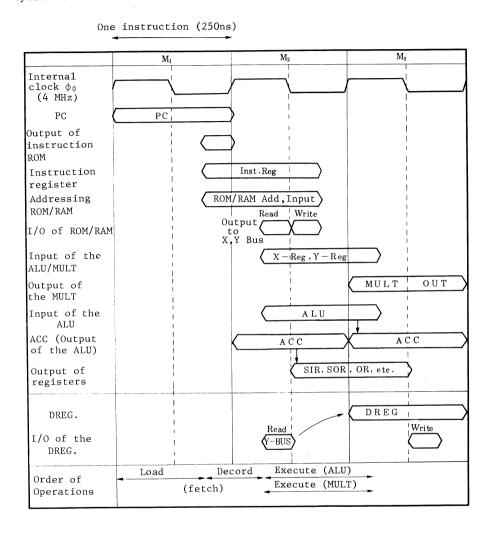

The HSP utilizes a pipeline control to realize a high-speed operation. This operation permits a full overlap of the instruction prefetch and execution as shown in Fig. 1.1.2. The results are saved for one instruction cycle and can be used in the next instruction cycle.

In the HSP, one instruction execution permits data read, arithmetic operation and data write, etc.

Fig. 1.1.2 PIPELINE CONTROL

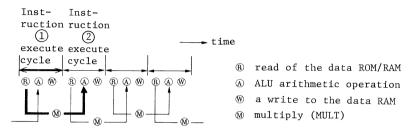

The HSP realizes a high throughput with a highly pipelined internal operation and a horizontal microprogram. Fig. 1.1.3 shows how the instructions are executed.

Though the result of multiplication is used in the next instruction cycle, the program with pipeline control permits the simultaneous operations of the ALU and MULT in appearance, thereby the high-speed operation is possible.

Fig. 1.1.3 ONE INSTRUCTION CYCLE

#### 1.2 APPLICATIONS

The HSP (HD61810) is typically used for the following signal processing.

- · Digital filter

- FFT

- · Digital PLL

- · Windowing

- · Modulation/demodulation

- · Waveform generation

- · Correlation

Its applications are described as below.

| 1. | TELECOMMUNICATIONS | • High-speed modems                            |

|----|--------------------|------------------------------------------------|

|    |                    | <ul> <li>Data transfer (PB,MF,etc.)</li> </ul> |

|    |                    | • Echo canceller                               |

|    |                    | <ul> <li>Modulation/demodulation</li> </ul>    |

|    |                    | • Adaptive equalizers                          |

|    |                    | · High-efficiency CODEC etc.                   |

| 2. | SPEECH PROCESSING  | · Speech synthesis                             |

|    |                    | • Speech analysis                              |

|    |                    | • Speech recognition                           |

|    |                    | • Voice mail                                   |

|    |                    | • Filter bank etc.                             |

| 3. | IMAGE PROCESSING   | · Pattern recognition etc.                     |

| 4. | HIGH-SPEED CONTROL | • Servo links etc.                             |

| 4. | HIGH-SPEED CONTROL | • Servo links etc.                             |

## SECTION 2 ARCHITECTURE

#### 2. ARCHITECTURE

#### 2.1 PIN FUNCTIONS

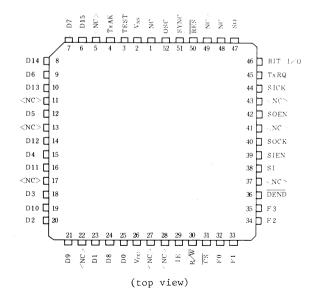

Fig. 2.1.1 and Fig. 2.1.2 show the HSP pin assignments.

|                          | _      |      |      |    |   |                          |

|--------------------------|--------|------|------|----|---|--------------------------|

| $V_{SS}$                 |        | 1    |      | 40 |   | OSC                      |

| TEST                     |        | 2    |      | 39 |   | SYNC                     |

| Tx AK                    |        | 3    |      | 38 |   | RES                      |

| D15                      |        | 4    |      | 37 |   | NC .                     |

| D7                       |        | 5    |      | 36 |   | SO                       |

| D14                      |        | 6    |      | 35 |   | BIT IZO                  |

| D6                       |        | 7    |      | 34 |   | TxRQ                     |

| D13                      |        | 8    |      | 33 |   | SICK                     |

| D5                       |        | 9    |      | 32 |   | SOEN                     |

| D12                      |        | 10   |      | 31 |   | SOCK                     |

| D4                       |        | 11   |      | 30 |   | SIEN                     |

| D11                      | $\Box$ | 12   |      | 29 | П | SI ·                     |

| D3                       |        | 13   |      | 28 |   | DEND                     |

| D10                      | $\Box$ | 14   |      | 27 |   | F3                       |

| D2                       |        | 15   |      | 26 |   | F2                       |

| D9                       |        | 16   |      | 25 |   | F1                       |

| D1                       |        | 17   |      | 24 |   | F0                       |

| D8                       |        | 18   |      | 23 | Ь | cs                       |

| D0                       |        | 19   |      | 22 |   | $R \diagup \overline{W}$ |

| $v_{t \boldsymbol{x}^*}$ |        | 20   |      | 21 | 5 | IE                       |

|                          | L      | / .  |      | Ų  |   |                          |

|                          |        | (top | viev | J) |   |                          |

(NOTE) Any line should not be connected to  $\ensuremath{^{<}NC^{>}}$  pins.

Fig. 2.1.1 DIC/DIP PACKAGE PIN ASSIGNMENT

(NOTE) Any-line should not be connected to <NC> pins.

Fig. 2.1.2 PLCC PACKAGE PIN ASSIGNMENT

#### • Pin Functions

(Each pin number corresponds to that of DIP package.)

| Signal      | Pin      | I/0 | Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------|----------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Vcc<br>Vss  | 20<br>1  |     | Power Supply 5V 0V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

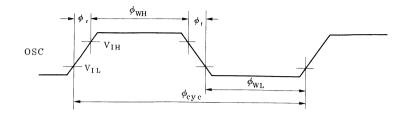

| OSC<br>SYNC | 40<br>39 | I   | Clocks The external clock used to operate the HSP. Clock rate; 16 MHz The internal clock of the HSP. Clock rate; 4 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|             |          |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

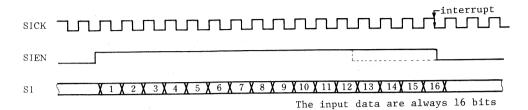

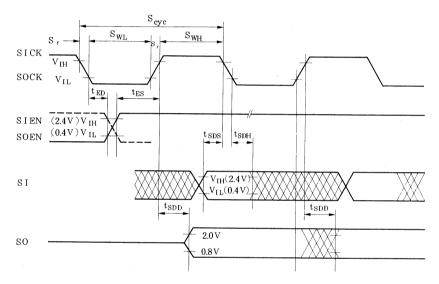

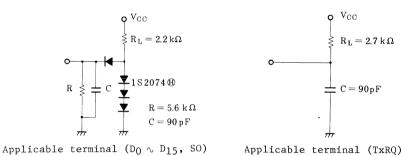

| SICK        | 33       | I   | Serial I/O Serial input clock. The serial data is input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| SIEN        | 30       | I   | synchronously with this clock.  Serial input enable. The serial input data is fetched into the serial input register with high level of SIEN. After the completion of a fetch, an interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| SI          | 29       | Ι   | can be generated in the HSP.  Serial data input. Enters the serial data into the  serial input register on the negative edge of SICK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

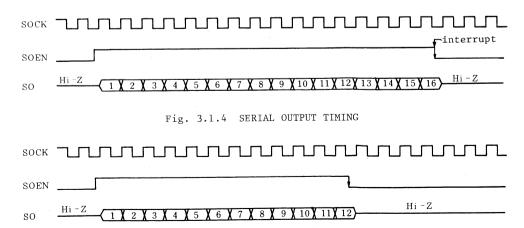

| SOCK        | 31       | I   | Serial output clock. The serial data is output synchronously with this clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| SOEN        | 32       | I   | Serial output enable. The serial output data is output from the serial output register with high level of SOEN.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| SO          | 36       | 0   | After the completion of output, an interrupt can be generated in the HSP on the negative edge of SOEN.  Serial data output. Three states. Outputs the serial data from the serial output register on the positive edge of SOCK. When SOEN is low, this pin goes to the high-impedance state.                                                                                                                                                                                                                                                                                                                                                 |

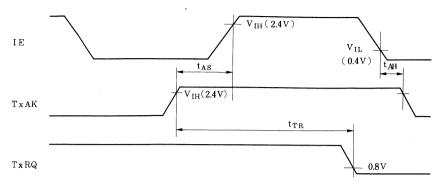

| TxAK        | 3        | Ι   | DMA Operation Transfer acknowledge DMA data transfer acknowledge                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| TxRQ        | 34       | 0   | input signal.  Transfer request, open drain output.  Used mainly in the DMA operation mode. This signal requests the external device (DMAC) to transfer data. If TxRQ (DMA transfer request bit) in the control register (CTR) is set, this pin goes to the high level, which requests a DMA service. This signal is automatically cleared with an input of TxAK. Even in the DMA operation mode, internal data transfer among the input/output register (IR/OR), an accumulator and memory is controlled by software.  TxRQ can be used as just an output pin in the non-DMA operation mode, and the status of TxRQ is altered by software. |

| DEND        | 28       | Ι   | DMA operation end signal. When $\overline{\text{DEND}}$ is active low, a DMA operation is completed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Signal                                                | Pin                                                                                    | 1/0              | Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

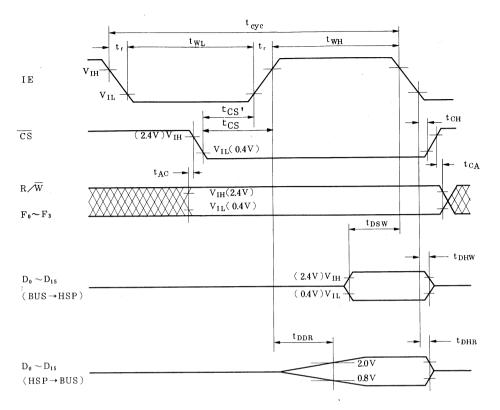

|-------------------------------------------------------|----------------------------------------------------------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

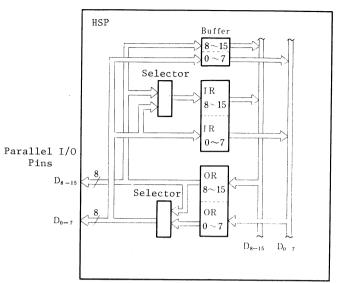

| DO D1 D2 D3 D4 D5 D6 D7 D8 D9 D10 D11 D12 D13 D14 D15 | 19<br>17<br>15<br>13<br>11<br>9<br>7<br>5<br>18<br>16<br>14<br>12<br>10<br>8<br>6<br>4 | 1/0              | Data Bus  Three states, bidirectional I/O ports. The direction of data bus depends on Read/Write (R/W) control signal. When CS (Chip Select) is high, these pins are placed in the high-impedance state.  The contents of the CTR and the function control pins (FO to F3) select 8-bit or 16-bit transfer mode.                                                                                                                                                                                                                                                                                                                                                                             |

| FO<br>F1<br>F2<br>F3<br>CS<br>R/W                     | 24<br>25<br>26<br>27<br>23<br>22                                                       | I<br>I<br>I<br>I | Parallel I/O Control  Function control. These signals select an internal register for the parallel data I/O. Connected to address buses of the microcomputer (6800/68000).  Chip select. The chip select signal enables the parallel I/O. When CS is active low, DO to D15, FO to F3, R/W and IE are valid.  Read/Write signal of the microcomputer. Data is read from the HSP with high level of this pin, and is written into the HSP with low level. Valid only when CS is active low.  Interface enable. Data transfer timing signal on data bus (DO to D15). The data on the data bus is transferred to the internal shift register with this signal. Valid only when CS is active low. |

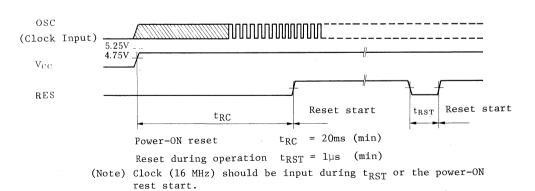

| TEST<br>RES                                           | 2 38                                                                                   | I<br>I           | Chip test pin (tied to GND).  Reset pin. The low level input of RES clears the program counter (PC). In the status register (STR), interrupt mask flag I <sub>M</sub> is set to disable an interrupt, and the I/O data transfer end flags (PF, SIF and SOF) are cleared. In the control register, DMA and TxRQ bits for DMA operation are cleared. When RES goes to high level, the program is executed from location 1. The instruction of location 0 is not executed.  (note) To reset, RES should remain low for more than 1 µs when OSC is applied.                                                                                                                                      |

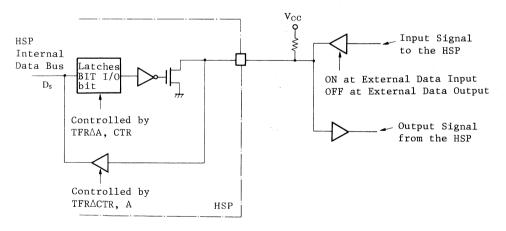

| BIT I/O                                               | 35                                                                                     | I/O              | Open drain output, 1-bit bidirectional I/O pin. The status of BIT I/O depends on software. Set the internal flip-flop of BIT I/O to a one before data input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

#### The Handling of HSP Unused Pins

When the HSP operates in the stand-alone mode, pins for control and parallel I/O are not used. Moreover, there are some cases when the serial I/O functions and DMA function are not used.

Each unused pin should be handled as follows.

Table 2.1.1 THE HANDLING OF HSP UNUSED PINS

| Functions     | Pins                                        | Pin No.                 | 1/0                       | Handling of Pins                                                                                                                                                                                |

|---------------|---------------------------------------------|-------------------------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Serial Input  | SI<br>SIEN<br>SICK                          | 29<br>30<br>33          | I<br>I<br>I               | Tie to Vcc/GND.<br>Tie to GND.<br>Tie to Vcc.                                                                                                                                                   |

| Serial Output | SO<br>SOEN<br>SOCK                          | 36<br>32<br>31          | 0<br>I<br>I               | Pull up/down by a resistor.<br>Tie to GND.<br>Tie to Vcc.                                                                                                                                       |

| DMA Operation | T×RQ*  T×AK  DEND                           | 34<br>3<br>28           | 0<br>I<br>I               | Pull down by a resistor.<br>Tie to GND.<br>Tie to Vcc.                                                                                                                                          |

| Bus I/O       | CS<br>IE<br>R/W<br>F0^F3<br>D0^D7<br>D8^D15 | 23<br>21<br>22<br>24-27 | I<br>I<br>I<br>I/O<br>I/O | Tie to Vcc. Tie to GND. Tie to Vcc. Tie to GND. Pull up/down by a resistor. Pull up/down by a resistor. (Note) Even in the byte transfer mode, D <sub>8</sub> \D <sub>15</sub> should be pulled |

| Others        | BIT I/O*<br>TEST<br>SYNC                    | 35<br>2<br>39           | I/0<br>I<br>0             | up/down by a resistor.  Pull down by a resistor.  Tie to GND. (Not for user)  Open                                                                                                              |

<sup>(</sup>Note 1) \* means open drain output. Connect a pull-up resistor to output data.

<sup>(</sup>Note 2) The pins tied to Vcc/GND can be connected to resistor.

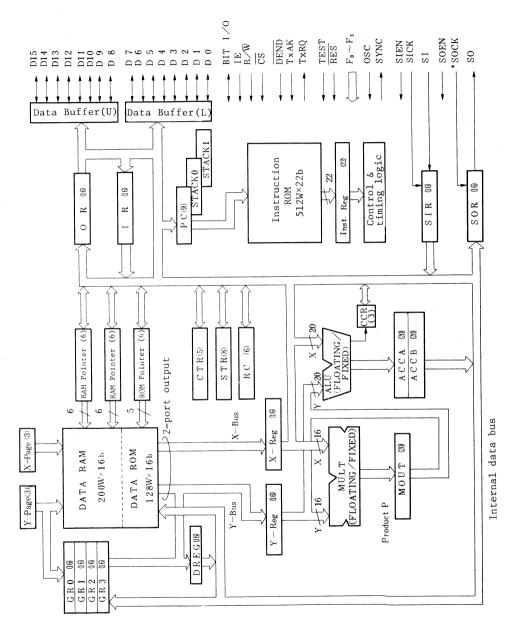

Fig. 2.2.1 HD61810 BLOCK DIAGRAM

#### 2.2 INTERNAL RESOURCES

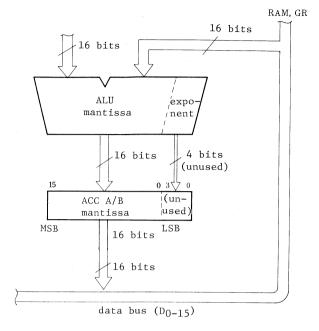

The HSP contains large capacity memories; a data RAM of 200 word  $\times$  16 bits, a data ROM of 128 words  $\times$  16 bits and an instruction ROM of 512 words  $\times$  22 bits, and contains dedicated multiplier and ALU which permit high-speed, high-accuracy floating point operation. The instruction ROM stores a comprehensive instruction set, which allows a wide range of applications.

The block diagram of the HSP is shown in Fig. 2.2.1. Each of the blocks is described in the following table.

| Input/Output Registers     |     |                                                                                                                                                                        |  |  |  |  |  |

|----------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|                            |     |                                                                                                                                                                        |  |  |  |  |  |

| Input Register             | IR  | l6-bit register. Data is input to this register through the external data bus (D0-D15).                                                                                |  |  |  |  |  |

| Output Register            | OR  | 16-bit register. Data is output from this register to the external data bus (D0-D15).                                                                                  |  |  |  |  |  |

| Serial Input<br>Register   | SIR | l6-bit shift register for serial data input. After a serial data is transferred from the SIR to an accumulator (ACCA or ACCB), the SIR is cleared.                     |  |  |  |  |  |

| Serial Output<br>Register  | SOR | l6-bit shift register for serial data output. If data has been transferred to the SOR through the internal data bus, the data is output to peripherals on a bit basis. |  |  |  |  |  |

|                            |     | Control Registers                                                                                                                                                      |  |  |  |  |  |

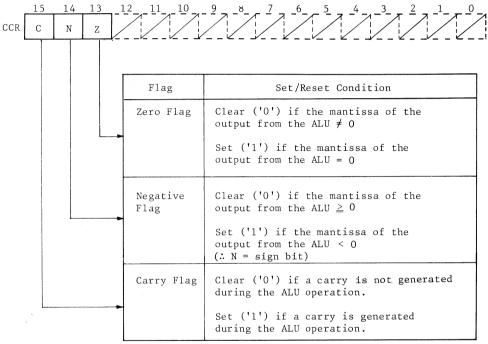

| Condition Code<br>Register | CCR | The CCR contains three flag bits; Carry (C), Negative (N), and Zero (Z). They indicate the results of ALU operation.                                                   |  |  |  |  |  |

| Status Register            | STR | The STR flags are individually set or cleared depending on the status of the HSP. The contents of the STR can be transferred to an accumulator.                        |  |  |  |  |  |

| Control Register           | CTR | The CTR is used to select the desired operating modes for the HSP. The CTR contents are determined by either the HSP                                                   |  |  |  |  |  |

| -                          |     | instructions or the MPU.                                                                                                                                               |  |  |  |  |  |

| r en | Inst             | ruction Controllers                                                                                                                                                                     |

|------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Instruction ROM                          | A WA             | A 512 word by 22 bit ROM. The instruction ROM stores instructions for the HSP. 22-bit instruction is transferred to the instruction register in parallel in a single instruction cycle. |

| Program Counter                          | PC               | The PC is a 9-bit address counter that is used to address the Instruction ROM. The PC generates the instruction ROM addresses through 511.                                              |

| Stack Registers                          | STACKO<br>STACKI | The stack registers are 9-bit registers that are used to save the PC contents. The contents of the PC is pushed onto these registers when a subroutine jump or an interrupt occurs.     |

| Repeat Counter                           | RC               | 6-bit down counter. The RC is used for repeated execution of an instruction and for the control of loops.                                                                               |

| Instruction<br>Register                  | Inst.<br>Reg.    | 22-bit buffer register. This register temporarily stores the instruction transferred from the instruction ROM.                                                                          |

|                                          | Intern           | al Memory Controllers                                                                                                                                                                   |

| Data RAM                                 |                  | A 200 word by 16 bit RAM.                                                                                                                                                               |

| Data ROM                                 |                  | A 128 word by 16 bit ROM.                                                                                                                                                               |

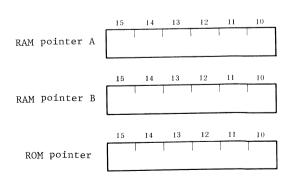

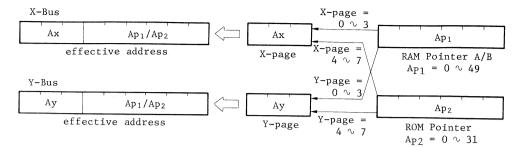

| RAM Pointer A<br>RAM Pointer B           | RA<br>RB         | These are 6-bit address pointers which are used to generate the data RAM address, combining with the contents of page address.                                                          |

| ROM Pointer                              | RO               | This is a 6-bit address pointer which is used to generate the data ROM address, combining with the contents of page address.                                                            |

| X and Y page<br>Address Pointers         | X/Y-<br>Page     | These are 3-bit buffer registers for a page address. The effective address for the data RAM or the data ROM consists of this address and the contents of the RAM/ROM pointer.           |

| General Registers                        | GR0-3            | 16-bit general purpose registers. The GRs can be used as working registers. Data is transferred to or from the GRs through the Y-Bus.                                                   |

|                                | Intern       | nal Memory Controllers                                                                                                                                                                            |

|--------------------------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

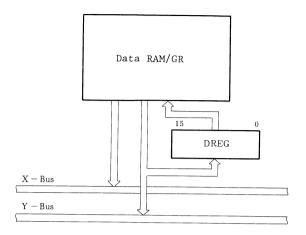

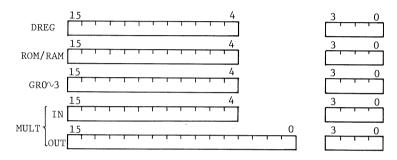

| Delay Register                 | DREG         | l6-bit register. The DREG holds the data to be transferred through the Y-but for a single instruction cycle period.                                                                               |

|                                | Aı           | rithmetic Elements                                                                                                                                                                                |

| Accumulator A<br>Accumulator B | ACCA<br>ACCB | 20-bit accumulators. The accumulators store the output from the ALU. Either the ACCA or ACCB is selected in response to the instructions.                                                         |

| Arithmetic Logic<br>Unit       | ALU          | The ALU performs arithmetic and logical operations. Either the fixed point operation or the floating point operation is selected depending on the instructions.                                   |

| Multiplier                     | MULT         | The MULT performs a multiply operation. Either the fixed point operation or the floating point operation is selected depending on the instructions.                                               |

| Multiplier<br>Input X-Register | X-Reg.       | l6-bit register. The X-Reg. holds the data transferred from the X-bus or the internal data bus during a multiply operation.                                                                       |

| Multiplier<br>Input Y-Register | Y-Reg.       | 16-bit register. The Y-Reg. holds the data transferred from the Y-bus or the internal data bus during a multiply operation.                                                                       |

| Multiplier<br>Output Register  | MOUT         | This is a 20-bit buffer register which holds<br>the output from the MULT for a single<br>instruction cycle period. This register<br>consists of a mantissa (16 bits) and an<br>exponent (4 bits). |

#### 2.3 MEMORY

#### 2.3.1 Configuration

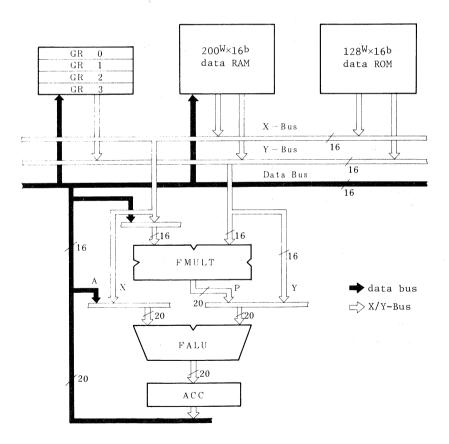

or GR through this bus.

The HSP has the following three data memories as shown in Fig. 2.3.1.

o Data RAM : 200 W × 16b

o Data ROM (for coefficient) :  $128 \text{ W} \times 16\text{b}$

o General Registers : 4 W × 16b

The words data can be transferred from these memories to the multiplier (FMULT) and ALU (FALU) in parallel through two buses; X- and Y-Bus. A data bus is also provided and the data is written into the data RAM

Program memory is a  $512~\mathrm{W}\times22\mathrm{b}$  on-chip ROM and stores instructions.

Fig. 2.3.1 DATA MEMORY CONFIGURATION

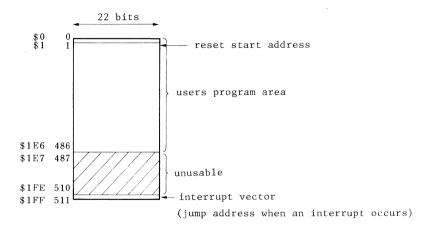

#### 2.3.2 Instruction ROM

The instruction ROM consists of up to 512 words of 22-bit width. A 22-bit instruction is read out to the instruction register during each instruction cycle. The program starts from location \$0, but the execution of the program starts from location \$1. When jumping to location \$0 during instruction execution, the program starts from location \$0 and the instruction of location \$0 is also executed.

Location \$1FF (the last address) is a vector address for interrupt. Thus, store jump instruction here for jump to an interrupt service routine. Locations \$1E7 through \$1FE are reserved for LSI testing purposes, so they should not be used for the user's program.

Fig. 2.3.2 INSTRUCTION ROM MEMORY MAP

#### 2.3.3 Data RAM

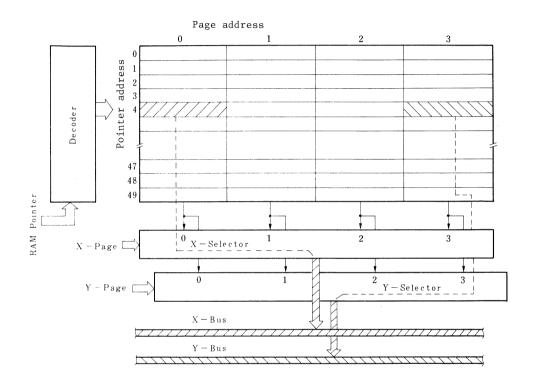

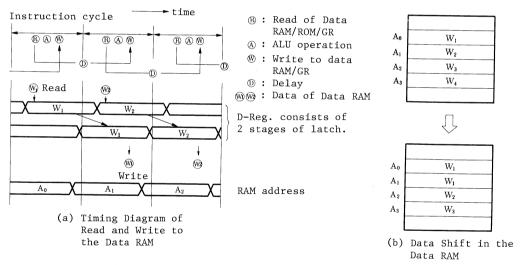

Data RAM consists of up to 200 words of 16-bit width and is divided into four pages (page address; 0 through 3). Each page consists of 50 words.

The data in the data RAM can be accessed through two ports. Two data of the different pages (X-page and Y-page) can be read in parallel if the pointer addressing mode is employed.

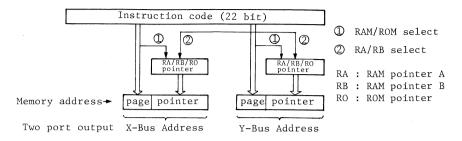

In the pointer addressing mode, 6 bits of the RAM pointer and 3-bit page address (X-/Y-page address) in the instruction code can be used as the data memory address. When accessing two data, the pointer addresses should be identical. (RAM pointer A and RAM pointer B cannot be used at the same time.) Fig. 2.3.4 illustrates data RAM memory access in the pointer addressing mode.

The page address specified in the X-page part of an instruction code is the X-Bus and that specified in the Y-page part to the Y-Bus a write operation is performed through the data bus to the data RAM address consisted of RAM pointer address and Y-page address. The contents of an accumulator or the DREG are written to the data RAM.

Fig. 2.3.3 DATA RAM MEMORY MAP

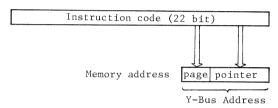

In the direct addressing mode, both the pointer address and the page address are contained in the instruction code. In this case, the data is output to Y-Bus.

See Section 2.4.8 for details of address pointers.

Fig. 2.3.4 MEMORY ACCESS OF DATA RAM (POINTER ADDRESSING MODE)

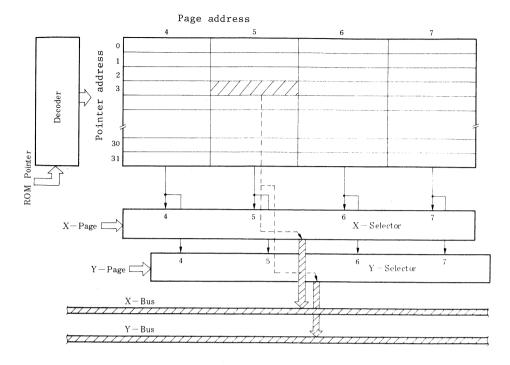

#### 2.3.4 Data ROM

Data ROM consists of up to 128 words of 16-bit width and is divided into four pages (page address; 4 through 7). Each page consists of 32 words. If the pointer addressing mode is employed, 6 bits of the ROM pointer and 3-bit page address (X-/Y-page address) in the instruction code are used to make an effective address.

The data RAM has two ports for output, while the data ROM has only one port. However, as shown in Fig. 2.3.6, one data can be output to both X-Bus and Y-Bus. Thus, two-data output from the data ROM does not allow the difference between the X- and Y-page addresses.

In the direct addressing mode, both the pointer address and the page address are contained in the instruction code. In this case, the data is output to Y-Bus.

When reading the data ROM and the data RAM at the same time, two data can be read from the different pointer addresses, because each data memory has its own pointer address.

Fig. 2.3.5 DATA ROM MEMORY MAP

Fig. 2.3.6 MEMORY ACCESS OF DATA ROM (POINTER ADDRESSING MODE)

#### 2.3.5 General Register (GR)

The HSP has four 16-bit general registers (GRO to 3) which are used as working registers.

If the pointer addressing mode is employed, the GR and data  ${\rm ROM/RAM}$  can be accessed at the same time.

The address of the GR is specified in the Y-page address part in the instruction code. The data in the GR is input/output through the Y-Bus.

| - | 16 bits | _ |

|---|---------|---|

|   | GR0     |   |

|   | GR1     |   |

|   | GR2     |   |

|   | GR3     | ı |

Fig. 2.3.7 GENERAL REGISTERS

#### 2.3.6 Memory Addressing Mode

There are two modes of data memory addressing; pointer addressing and direct addressing.

#### (1) Pointer addressing mode

Pointer addressing uses the page address (0 through 7 page) and the pointer address as the data memory address. Page address is contained in the instruction code, and the pointer address is determined by each address pointer (RA/RB/RO).

In this mode, the X-Bus output and Y-Bus output are as follows: o The data RAM and data ROM are accessed.

o The data RAM/ROM and GR are accessed.

The pointer addressing mode is available for accessing two-word data during the product sum operation, reading data from sequential addresses, etc.

#### (2) Direct addressing mode

In direct addressing, nine bits of the instruction code specify data RAM/ROM address (page address and pointer address). The direct addressing mode is available for multiplying one-word data in the data ROM/RAM by data in an accumulator, or reading data from discrete addresses.

Pointer part is specified by ROM/RAM pointer indirectly.

#### (a) Pointer addressing mode

Memory address is specified directly.

#### (b) Direct addressing mode

Fig. 2.3.8 MEMORY ADDRESSING MODE

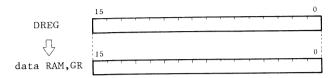

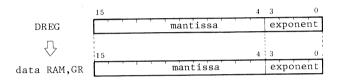

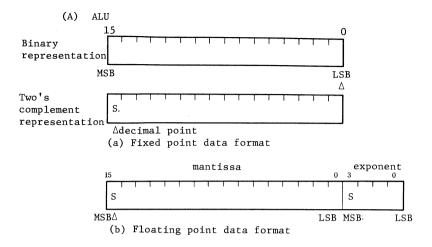

#### 2.3.7 Memory Data Format

Fig. 2.3.9 details data formats in the data ROM/RAM and GR.

Note that in floating point data form the twelve leftmost bits of the l6-bit mantissa are transferred from an accumulator to the data memory.

Fig. 2.3.9 DATA FORMAT

#### 2.3.8 Precaution in Using the Data ROM/RAM

- (1) The data RAM (and registers, if necessary) should be cleared by software after power on to prevent the oscillation of the digital filter, etc. The data RAM cannot be cleared at reset.

- (2) Location 31 (in page 7) of the data ROM is reserved by the HSP emulator system for program development. Special attention is needed not to use this location when using the emulator system.

#### 2.4 REGISTERS

#### 2.4.1 Program Counter (PC)

The PC is a 9-bit register which contains the address of the next instruction to be executed. The PC can generate the instruction ROM addresses in the range from 0 through 511.

The MPU can set the instruction ROM addresses 0 through 255 in the PC through the external data bus. In this case, however, the instruction execution starts from the next address to the specified one.

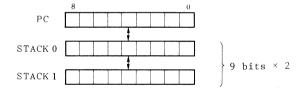

#### 2.4.2 Stack Registers (STACKO and STACKI)

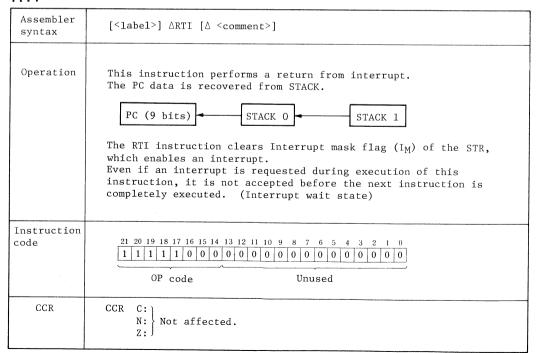

The STACKO and the STACK1 are 9-bit registers. The contents of the PC are pushed onto the stack registers when a subroutine jump or an interrupt occurs.

The HSP provides two stack registers, allowing two nesting levels.

Fig. 2.4.1 ARRANGEMENT OF THE STACK REGISTERS

#### 2.4.3 Accumulators (ACCA and ACCB)

The HSP has two 20-bit accumulators (ACCA and ACCB). Either of the accumulators is selected by the accumulator select bit in the instruction code.

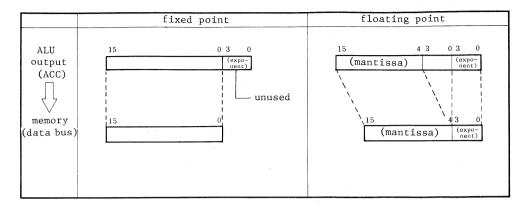

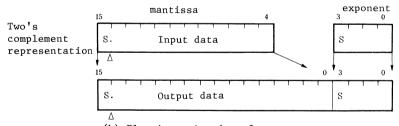

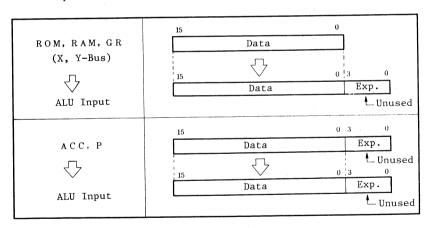

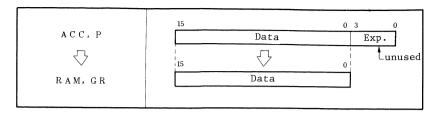

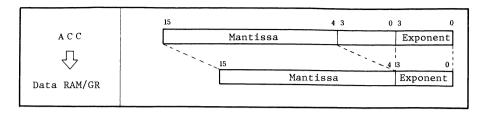

The accumulators store the output from the ALU. Fig. 2.4.2 and Fig. 2.4.3 show the input/output of the accumulators for the fixed point operation and the floating point operation respectively. When a floating point data is transferred from an accumulator to the data RAM or the GRs, the lower four bits of the mantissa is truncated.

Since a floating point data consists of 20 bits, it occupies two words of the data RAM or two GRs. A transfer of a floating point data between an accumulator and the data RAM (or the GRs) is performed in the following procedures.

- o To save the contents of an accumulator in the data RAM or the GRs,

- (1) transfer a mantissa (16 bits) of the floating point data from the accumulator to a data RAM (or GR) address 1 in the fixed point representation.

- (2) then transfer the same data into the next data RAM (or the next GR) address ② in the floating point representation.

- o To transfer the contents of the data RAM or the GRs to an accumulator,

- (1) Transfer the contents of the data RAM (or GR) address 1 to the accumulator.

- (2) Converts the contents of the accumulator to a floating point data using the contents of the data RAM (or GR) address ② as a scaling constant.

Fig. 2.4.2 INPUT/OUTPUT OF THE ACCUMULATORS FOR THE FIXED POINT ARITHMETIC OPERATION

Fig. 2.4.3 INPUT/OUTPUT OF THE ACCUMULATORS FOR THE FLOATING POINT ARITHMETIC OPERATION

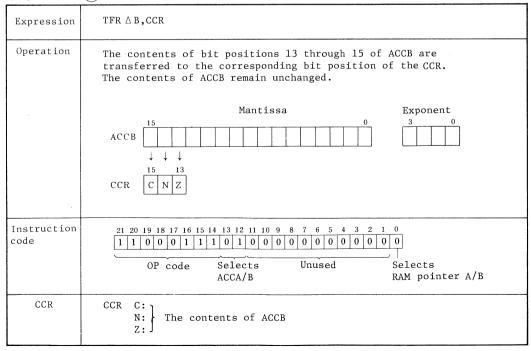

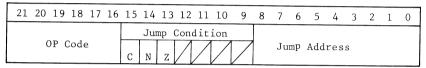

#### 2.4.4 Condition Code Register (CCR)

The CCR contains three flag bits; Carry (C), Negative (N) and Zero (Z). They indicate results of the ALU operation.

The CCR is connected to the D13 to D15 bits of the internal data bus. which allows the transfer of data between the CCR and the accumulators in response to the instructions.

o All of the CCR bits are affected by the fixed point operation.

o Z and N are affected by the floating point operation.

For details of the C flag bit, see 5.2 'INSTRUCTION SET'.

Fig. 2.4.4 CCR SET/RESET CONDITION

## 2.4.5 Control Register (CTR)

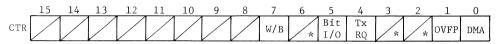

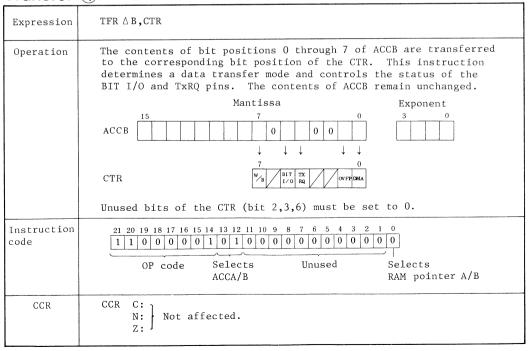

The CTR can be used to determine the desired operating mode for the HSP. Dedicated instructions transfer data from the accumulator to the CTR. The MPU can also input data to the CTR through parallel I/O pins (DO - D15). During reset, the DMA bit and the TxRQ bit are cleared but the others are undefined.

The CTR is connected to the DO to D7 of the internal data bus.

Table 2.4.1 FUNCTIONS OF THE CTR

| Bit | Name                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Function                                         | Descriptions                                                                                                                                                                                                                                                                                              |  |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 0   | DMA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Parallel I/O<br>Data Transfer<br>Mode Select bit | • Selection of the mode for data transfer through the parallel I/O ports.  1: DMA operation mode  0: Non-DMA operation mode                                                                                                                                                                               |  |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                  | This bit must be cleared during a usual data transfer. Even in the DMA operation mode, the transfer of data through the parallel I/O ports must be accomplished by the HSP instructions.                                                                                                                  |  |

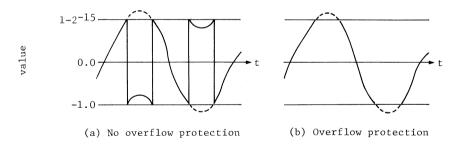

| 1   | 1 OVFP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Overflow<br>Protection bit                       | • Protection against overflows.                                                                                                                                                                                                                                                                           |  |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Trotection bit                                   | If an overflow occurs during an ALU operation, the result is fixed to the maximum value.                                                                                                                                                                                                                  |  |

|     | The second secon |                                                  | <ul><li>l: Performing a protection against overflow.</li><li>0: Not performing a protection against overflow.</li></ul>                                                                                                                                                                                   |  |

| 4   | TxRQ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | DMA Operation<br>Request bit                     | • Request for DMA operation.  This bit is set to request a DMA transfer in the DMA operation mode.  The TxAK input clears this bit and then it is set automatically. However, after the DEND input, this bit remains clear. In the non-DMA operation mode, the TxRQ can be used as a programmable output. |  |

| 5   | BIT<br>I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Bit I/O bit                                      | • Input and output of the BIT I/O pin.                                                                                                                                                                                                                                                                    |  |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                  | This bit controls the input/output of the BIT I/O pin. When using the BIT I/O pin as an output, the user must write data directly to this register. When using the bit as an input, he must write a 1 and then data in this register.                                                                     |  |

| Bit | Name | Function      | Descriptions                                                                                                                                    |

|-----|------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | W/B  | Word/Byte bit | o Selection of the size of the data transfer-<br>red through parallel I/O ports.  1: Word (16-bit) data is used.  0: Byte (8-bit) data is used. |

<sup>\*</sup> Os must be written in the unused bits of the CTR, but 1s are read from these bits.

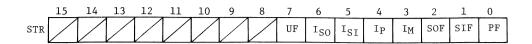

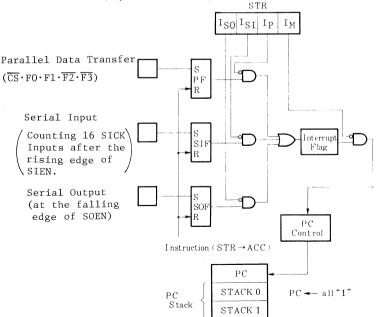

# 2.4.6 Status Register (STR)

The STR indicates the current  $\ensuremath{\mathsf{HSP}}$  information and controls the  $\ensuremath{\mathsf{HSP}}$  operation.

The contents of this register are transferred to the accumulator by the TFR instructions (TFRASTR,A and TFRASTR,B). After the transfer of data from the STR to the accumulator, the SOF, SIF and PF bits are cleared.

In addition, the contents of the accumulator can be transferred into the UF,  $I_{SO}$ ,  $I_{SI}$ ,  $I_P$  and  $I_M$  bits by the instructions (TFRAA, STR and TFRAB, STR).

The STR is connected to the low-order byte of the internal data bus (DO-D7). During reset, the  $\rm I_M$  bit is set, the PF, SIF and SOF are cleared and the other bits are undefined.

Table 2.4.2 FUNCTIONS OF THE STR

| Bit | Name | Function                                   | Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----|------|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | PF   | Parallel I/O<br>data transfer<br>end flag  | The PF bit is a read-only bit which is set by the CS input during data transfer through the DO-D15. If the data transfer is performed on a byte basis, the PF bit is set by the CS input during the transfer of the high-order byte. If interrupts are enabled, an interrupt occurs when this bit is set. The PF bit can be set even when interrupts are disabled. The data transfer from the STR to the accumulators clears the PF. |

| 1   | SIF  | Serial input<br>data transfer<br>end flag  | The SIF bit is a read-only bit which is set to indicate that a serial input has been completed. If interrupts are enabled, an interrupt occurs when this bit is set. This bit can be set even when interrupts are disabled. The data transfer from the STR to the accumulator clears the SIF.                                                                                                                                        |

| 2   | SOF  | Serial output<br>data transfer<br>end flag | The SOF is a read-only bit which is set to indicate that a serial output has been completed. If interrupts are enabled, an interrupt occurs when this bit is set. This bit can be set even when interrupts are disabled. The data transfer from the STR to the accumulator clears the SOF bit.                                                                                                                                       |

Table 2.4.2 FUNCTIONS OF THE STR (cont'd)

| Bit | Name            | Function                               | Descriptions                                                                                                                                                                                                                                                                  |

|-----|-----------------|----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3   | I <sub>M</sub>  | Interrupt mask<br>bit                  | When an interrupt occurs, the $I_M$ bit is automatically set to prevent additional interrupts. The $I_M$ bit is cleared by the RTI instruction. This bit is also set or cleared in response to the data transfer instructions of TFR $\Delta A$ ,STR and TFR $\Delta B$ ,STR. |

| 4   | IP              | Parallel I/O<br>interrupt mask<br>bit  | The Ip bit is set to disable interrupts occuring after the completion of a data transfer through the parallel I/O ports. The Ip bit is also set or cleared in response to the data transfer instructions of TFR $\triangle$ A,STR and TFR $\triangle$ B,STR.                  |

| 5   | <sup>I</sup> SI | Serial input<br>interrupt mask<br>bit  | The Isi bit is set to disable interrupts occurring after the completion of serial input. This bit is set or cleared in response to the data transfer instructions of TFR $\triangle$ A,STR and TFR $\triangle$ B,STR.                                                         |

| 6   | I <sub>SO</sub> | Serial output<br>interrupt mask<br>bit | The $I_{SO}$ bit is set to disable interrupts occuring after the completion of serial output. This bit is set or cleared in response to the data transfer instructions of TFR $\triangle$ A,STR and TFR $\triangle$ B,STR.                                                    |

| 7   | UF              | User's bit                             | The UF bit is an optional bit. This bit is set or cleared in response to the data transfer instructions of TFR $\triangle$ A,STR and TFR $\triangle$ B,STR.                                                                                                                   |

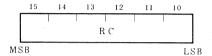

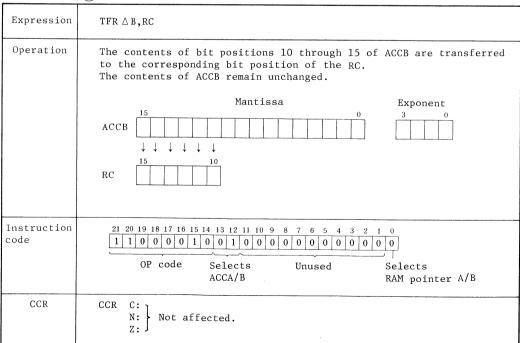

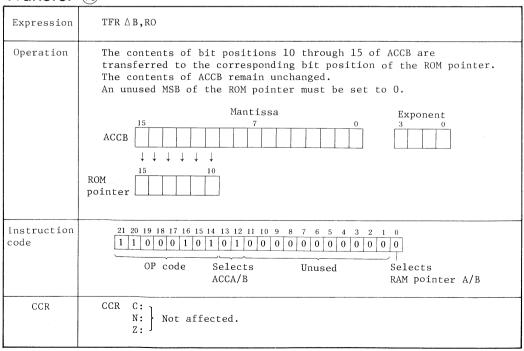

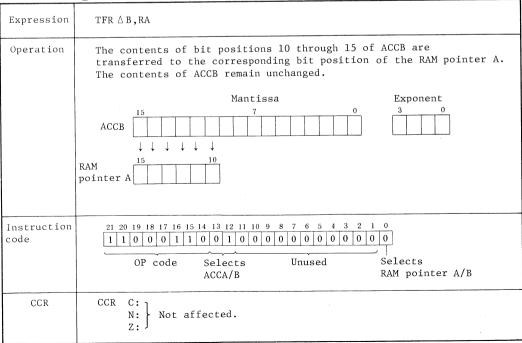

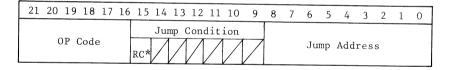

#### 2.4.7 Repeat Counter (RC)

The RC can be used for the repeated execution of the same program step in response to the repeat instructions or for the execution of loops in response to the jump instructions. This counter reduces the number of the program steps for repeated product/sum operations, which leads data processing time to be reduced.

The RC consists of six bits connected to D10 through D15 of the internal data bus. The user can set a value of 0 to 63 in the RC.

Fig. 2.4.5 REPEAT COUNTER

The following programs contain the repeated operations using the RC.

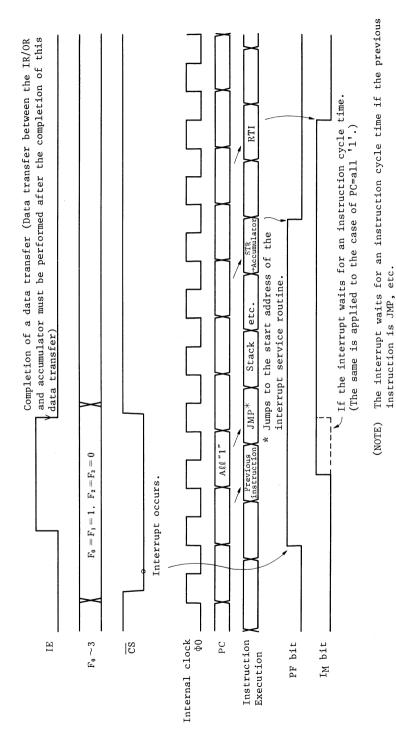

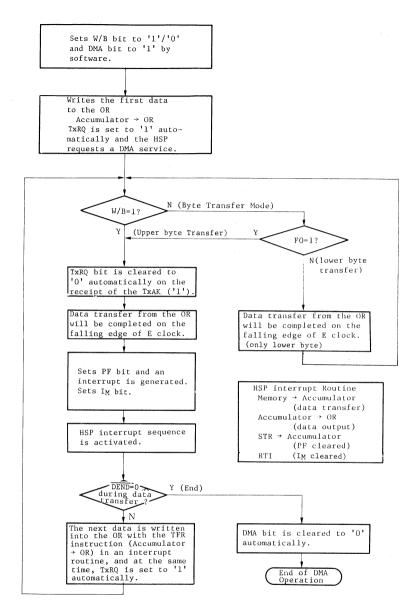

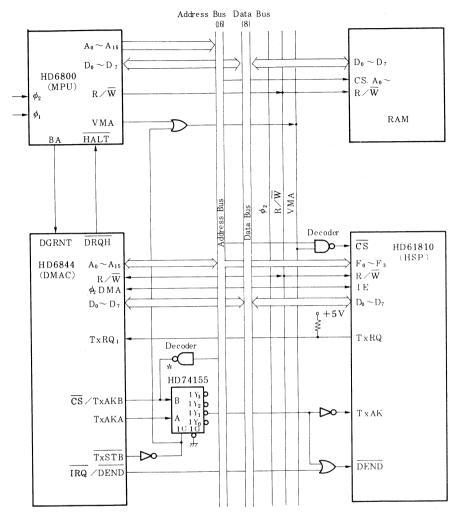

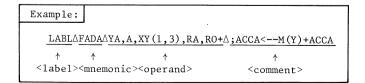

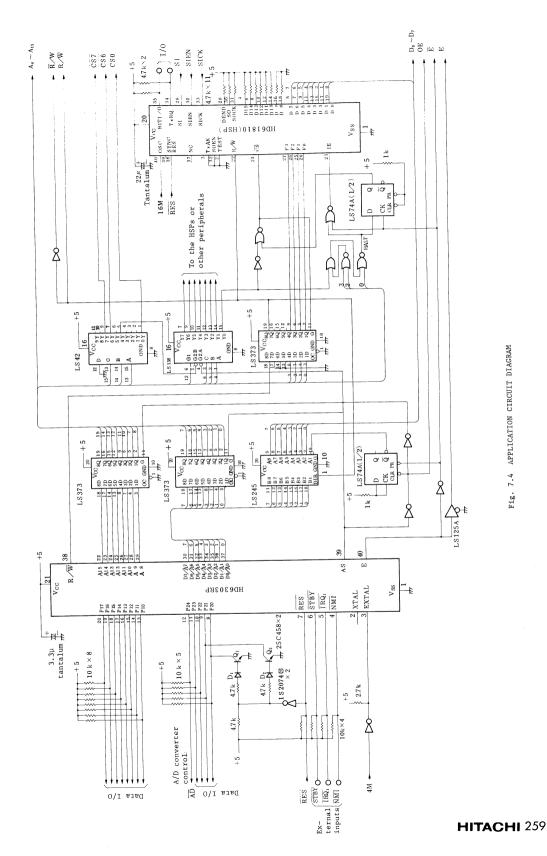

Example (1) Repeated operation by the repeat instructions